Модуль УМПК-80/МИ2: Узел индикации канала A (CDW)

- Добавлен: 24.01.2023

- Размер: 436 KB

- Закачек: 0

Описание

Состав проекта

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- Компас или КОМПАС-3D Viewer

- Microsoft Word

Дополнительная информация

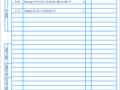

![]() Перечень элементов.cdw

Перечень элементов.cdw

ГОУ ОГУ 230104.6009.03

DD1 Микросхема К589ИР12 бкО.348.289 ТУ4 1

HL1 HL8 Светодиод АЛ307ГМ ААО.336.076.ТУ 8

X2 Розетка РС-16-1 АГО.364.003 ТУ 2"

![]() Содержание1.doc

Содержание1.doc

2 Назначение модуля УМПК-80МИ2 4

3 Описание микросхем входящих в модуль .5

4 Структурная схема модуля УМПК-80МИ2 ..7

5 Функциональная схема модуля УМПК-80МИ2 .8

6 Описание работы модуля по функциональной схеме .9

Узел индикации канала А .12

1 Назначение функционального узла ..12

2. Описание микросхем входящих в функциональный модуль 12

2.1 Микросхема К589ИР12 ..12

3 Функциональная схема узла .18

4 Описание принципиальной электрической схемы узла .18

5 Расчет временных задержек в схеме функционального узла .19

6 Расчет мощности потребляемой функциональным узлом от источника

Список использованных источников .21

Приложение А Схема принципиальная электрическая 22

Приложение Б Перечень элементов . 22

![]() Электрическая принципиальная схема.cdw

Электрическая принципиальная схема.cdw

Узел индикации канала А

Схема электрическая принципиальная

ГОУ ОГУ 2130104.6009.03 ЭЭ

DD1 Микросхема КР589ИР12 бкО.348.289 ТУ4 1

HL1 HL8 Светодиод АЛ307БМ ААО.336.076.ТУ 8

XP2 Розетка РС-16-1 АГО.364.003 ТУ 2"

![]() Титульный.doc

Титульный.doc

Государственное образовательное учреждение

Высшего профессионального образования

ОРЕНБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

Кафедра систем автоматизации производства

Расчетно-графическая работа

по дисциплине: “Схемотехника”

Узел индикации канала A

студент группы 06САП

![]() Содержание.doc

Содержание.doc

2 Назначение модуля УМПК-80МИ2 4

3 Описание микросхем входящих в модуль .5

4 Структурная схема модуля УМПК-80МИ2 ..7

5 Функциональная схема модуля УМПК-80МИ2 .8

6 Описание работы модуля по функциональной схеме .9

Узел индикации канала А .12

1 Назначение функционального узла ..12

2. Описание микросхем входящих в функциональный модуль 12

2.1 Микросхема К589ИР12 ..12

3 Функциональная схема узла .18

4 Описание принципиальной электрической схемы узла .18

5 Расчет временных задержек в схеме функционального узла .19

6 Расчет мощности потребляемой функциональным узлом от источника

Список использованных источников .21

Приложение А Схема принципиальная электрическая 22

![]() Введение.doc

Введение.doc

Промышленностью освоены и выпускаются много типов микропроцессоров благодаря которым обеспечена реализация цифровых методов обработки информации.

Для обработки сигналов разработана большая номенклатура микросхем среди которых можно отметить генераторы усилители аналого-цифровые и цифро-аналоговые преобразователи модуляторы компараторы переключатели тока и напряжения элементы выборки и хранения фильтры центральные процессорные элементы устройства управления вводом-выводом параллельные и последовательные интерфейсы контроллеры прямого доступа к памяти магистральные приемопередатчики блоки приоритетного прерывания запоминающие устройства многофункциональные синхронизирующие устройства программируемые таймеры и т.п.

Большинство перечисленных схем устройств являются функциональными составными частями микропроцессорных комплектов в значительной степени определяя архитектуру микропроцессорных систем управления и ЭВМ используемых в составе систем управления.

При этом особого внимания требуют вопросы согласования (сопряжения) основных функциональных устройств между собой в составе микропроцессорной системы управления и ЭВМ от которого в первую очередь зависит полнота реализации каждым устройством своих функциональных возможностей.

Исходными данными является учебный стенд УМПК-80МИ-2 и его функциональный узел индикации канала С.

2 Назначение модуля УМПК-80МИ2

Модуль УМПК-80МИ2 предназначен для исследования режимов работы больших интегральных схем КР580ВВ55А и может также использован для сопряжения микроЭВМ с устройствами ввода и вывода параллельной информации работающими в синхронном и асинхронном режимах сопряжения двух микроЭВМ. Связь микроЭВМ построенная на основе микропроцессорного комплекта серии К580 с устройствами принимающими и передающими информацию в параллельном коде (цифро-аналоговыми и аналого-цифровыми преобразователями датчиками индикаторами и т.п.) осуществляется с помощью больших интегральных схем (БИС) программируемого параллельного интерфейса КР580ВВ55А которая позволяет строить схемы универсальных параллельных интерфейсов.

Модуль УМПК-80МИ2 позволяет:

- изучать методы обмена данными в параллельном коде между микроЭВМ и периферийных устройств систем управления;

- исследовать методы программирования и особенности больших интегральных схем;

- изучать функционирование больших интегральных схем КР580ВВ55 в различных режимах работы;

- отлаживать рабочие программы предназначенные для постановки в разрабатываемые устройства.

Модуль дает возможность изучить программирование и функционирования больших интегральных схем входящих в его состав алгоритмы обмена информации с различными периферийными устройствами а также расширить возможности микроЭВМ за счет их подключения.

3 Описание микросхем входящих в модуль

Описание микросхем которые входят в модуль представлены в таблице 1.

Таблица 1 – Краткое описание микросхем

Программируемое устройство для ввода-вывода параллельной информации (БИС параллельного интерфейса)

логических элемента 2И-НЕ

Двунаправленный 8-ми разрядный шинный формирователь

D-триггера с прямыми и инверсными выходами

Продолжение таблицы 1

Двунаправленный 8-ми разрядный шинный формирователь

Многорежимный буферный регистр

Логический элемент 8И-НЕ

Двоичный дешифратор на 8 направлений

Шинный формирователь

логических элемента 2И

логических элемента НЕ

4 Структурная схема модуля УМПК-80МИ2

Рисунок 1 – Структурная схема модуля УМПК-80МИ2

Ниже представлено поблочное описание состава модуля по структурной схеме:

- блок параллельного интерфейса БИС КР580ВВ55А входной буфер данных на ИС КР580ВА86;

- блок дешифратора адреса - микросхемы К555ЛН1 К555ЛА3 К555ЛА2 К555ИД7;

- блок индикации внутреннего состояния триггеров разрешения прерываний - микросхема К555ТМ8;

- блок индикации управляющего слова– микросхемы К555ЛА3 К589ИР12;

- блок ввода канала А - шинный формирователь К589АП16;

- блок выбора режима работы – микросхема К555ЛН1;

- блок индикации канала А - буферный регистр К589ИР12;

- блок индикации канала С - микросхемы К555ЛА3 К555ЛИ1 шинный формирователь К589АП16;

- блок формирования управляющего сигнала микросхемы К555ЛН1 К555ЛИ1;

- блок ввода канала В – микросхема К555ЛН1 шинный формирователь К589АП16.

5 Функциональная схема модуля УМПК-80МИ2

Рисунок 2 - Функциональная схема модуля УМПК-80МИ2

Сокращения принятые на функциональной схеме приведены в таблице 2

Таблица 2 – Обозначения на функциональной схеме

Параллельный интерфейс

Чтении и запись данных

Формирование сигналов выборки устройств и синхронизации осциллографа

Схема индикации управляющего слова

Отображение состояния регистра управляющего слова ППИ

Схема индикации состояния внутренних триггеров разрешения прерывания

Отображает информацию о триггерах разрешения прерывания каналов А и В

Устройство ввода канала А

Создает необходимые входные сигналы для канала А

Устройство индикации канала А

Отображение информации записанной в регистр канала А

Устройство ввода канала В

Побитный ввод данных

Устройство ввода канала С

Создает необходимые входные сигналы для канала С

Устройство индикации канала С

Отображает информацию на выходах канала С

Устройство формирования управляющих сигналов

Ручная имитация сигналов внешних устройств при обмене информации

Схема выбора режима работы

Реализация нескольких режимов работы: «Блокировка» «Работа» «Автоматический» «Ручной».

6 Описание работы модуля по функциональной схеме

В схему параллельного интерфейса входят БИС ППИ КР580ВВ55 и входной буфер данных на ИС КР580ВА86 направление передачи данных через который по входу Т определяет системный сигнал управления IOR. При низком уровне этого сигнала (в момент выполнения команды IN) буфер открывается в направлении от параллельного периферийного интерфейса к микроЭВМ и производится чтение одного из внутренних регистров параллельного периферийного интерфейса. При выполнении команды OUT буфер открывается в обратном направлении и информация с магистрали данных микроЭВМ записывается в один из внутренних регистров параллельного периферийного интерфейса. Номер регистра определяется информацией на адресных входах А0 и А1.

Дешифратор адреса использует формирования сигналов выборки устройства и синхронизирует полученный сигнал с осциллографом. При обращении микроЭВМ к устройствам вводавывода формируются следующие сигналы:

а) запись в устройство вводавывода с адресом BOH – сигнала выбора параллельного периферийного интерфейса низкого уровня и стробирования записи в регистр индикации канала А. Информация записывается в канал А параллельного периферийного интерфейса одновременно записывается в регистр индикации канала А D18 и отображается с помощью светодиодов HL17

б) запись в устройство вводавывода с адресом B1H и B2H – выборка параллельного периферийного интерфейса и буфера данных;

г) запись в устройство вводавывода с адресом B3H – выборка в параллельного периферийного интерфейса выборка буфера данных и стробирование записи в регистр индикации управляющего слова по которому данные записанные в регистр управления параллельного периферийного интерфейса одновременно записываются в регистр D6 и отображаются на светодиодах HL4 HL11 этот сигнал кроме того выведен на соединитель Х2 и может подаваться на вход внешней синхронизации осциллографа при наблюдении внешних диаграмм;

д) чтение на устройстве вводавывода с адресами B0H B1H B3H – выборка параллельного периферийного интерфейса и буфера данных;

е) чтение из устройства вводавывода с адресом B2H - выборка параллельного периферийного интерфейса буфера данных и стробирования записи в триггер D4 по которому при чтении из регистра канала С информация о состоянии разрядов С2 С4 С6 записывают в регистр D4 и отображается на светодиодах HL1 HL3.

Дополнительную информацию о состоянии ППИ дает регистр К555ИД7 в котором фиксируются разряды 2 4 6 порта С т.е. те разряды порта с помощью которых устанавливается (разрешается) или запрещается формирование сигналов запроса прерываний INT. Эти разряды устанавливаются при программировании БИС с помощью управляющего слова BIT SETRESET.

Ввод данных для каналов А и В в режимах 1 и 2 осуществляется от соответствующих переключателей через буферные усилители. Замкнутое состояние соответствует логическому нулю разомкнутое состояние - логической единице.

Выбираются буферные усилители низким уровнем замкнутого переключателя. Для канала А усилители К589ИР12 в нормальном состоянии открыты на вывод информации и переключаются на ввод данных низким уровнем сигнала при нажатии на кнопку. Направление передачи через буферы канала В определяется разрядом D1 управляющего слова программирующего канал В на ввод или вывод.

В модуле предусмотрена индикация данных записанных в регистрах каналов А и С. Схема индикации канала А может работать в двух режимах. В автоматическом режиме переключатель замкнут и обеспечивает высокий уровень на входе разрешения записи регистра со статическим управлением. Режим ручного ввода позволяет отображать информацию в режимах 1 и 2 канала А. Запись в регистр стробируется сигналом поступающим из устройства формирования управляющих сигналов при нажатии на кнопку.

Схема индикации канала С включает буферные усилители и светодиоды. Усилители включены на вывод информации - на входе BS высокий уровень (передача с шины В на шину С) что обеспечивает постоянный контроль за состоянием порта С (при замкнутом переключателе).

Устройство формирования управляющих сигналов позволяет имитировать о помощью кнопок сигналы от внешних устройств при обмене информацией в режимах 1 и 2 - стробы чтения каналов А и В формируемые кнопками и сигналы подтверждения записи каналов А и В.

Схема выбора режима работы позволяет дополнительно реализовать следующие возможности при обмене данными через ППИ:

БЛОКИРОВКА". Переключатель разомкнут. В этом режиме отключаются буферные элементы что дает ППИ возможность работать о внешними устройствами через разъем Х2.

РАБОТА". Переключатель замкнут. Буферные элементы подключены (на входах CS и ОЕ активный низкий уровень) и позволяют вводить информацию с помощью устройств ввода каналов и отображать выводимую информацию на светодиодах.

АВТОМАТИЧЕСКИЙ" и "РУЧНОЙ" устанавливаются для канала А в режиме индикации и выбираются с помощью переключателя замкнутое состояние которого обеспечивает высокий уровень на входе С регистра индикации канала А (режим "АВТОМАТИЧЕСКИЙ") разомкнутое -"РУЧНОЙ".

В автоматическом режиме постоянно индицируются данные в канале А в ручном режиме запись в регистр индикации осуществляется только по сигналу кнопки или программно через разряд D0 канала В.

Узел индикации канала А

1 Назначение функционального узла

Устройство индикации канала А предназначено для отображения информации записанной в регистр канала А и может работать в двух режимах. Автоматический режим (переключатель SA21 соединяет вход 5 элемента DD16.3 с обычной шиной) позволяет отображать выходные данные канала А которые приходят с выхода канала на выход регистра DD18 и отображаются с помощью светодиодов HL17 HL24.

2 Описание микросхем входящих в функциональный узел

В состав узла входят:

- 8 резистивных элементов;

- микросхема К589ИР12.

2.1 Микросхема К589ИР12

Микросхема представляет собой многофункциональный буферный регистр и предназначена для подключения различных внешних устройств микропроцессорного вычислительного устройства с помощью единой магистрали данных. Данная микросхема является универсальным 8-ми разрядным регистром с выходами имеющими 3 состояния. Он имеет встроенную логическую схему и независимый триггер для формирования запроса прерывания центрального процессора. Может реализовать множество различных типовых устройств таких как: простые регистры данных буферный регистр со стробированием данных мультиплексоры двунаправленные шинные формирователи прерыватели каналов вводавывода.

Микросхема состоит из 8-ми информационных D-триггеров 8-ми выходных устройств с тремя устойчивыми состояниями и отдельного D-триггера для формирования запросов прерывания и гибкой схемы управления режимами работы регистра.

Информационные D-триггеры повторяют входную информацию при высоком уровне входного сигнала MD и а также при EW = 1 и MD = 1 при низком уровне сигнала на входе EW и при MD = 0 происходит хранение входной информации. Выходы каждого информационного триггера соединяет с выходным буферными каскадами с тремя установившимися состояниями. Внутренняя шина выдачи информации PB стробирует каждый выходной буферный каскад. При наличии логической 1 шине PB выходные буферные каскады разблокированы и данные поступают на выходы соответствующей линии выходных данных (Q1 – Q8). Условие выработки появления сигнала – . Внутренняя шина записи информации ЕW стробирует каждый триггер регистра. При наличии логической

на шине происходит запись информации в триггер соответствующий входной информационной шине (D1 – D2). Условие появления сигнала:

Информация в триггерах многорежимного буферного регистра обнуляется асинхронно входным сигналом CLR.

В многорежимном буферном регистре управляющими входами являются CS2 MD и EW эти входы используются для управления выборкой устройств информационного регистра состояния выходных буферных каскадов и триггером запроса на прерывание.

Выборкой кристалла управляют входы CS1 и CS2. при наличии логической 1 на входе CS2 устройство выбрано сигнал выборки кристалла (CS1 и CS2) используются как синхросигнал для асинхронной установки состояния выходных буферных каскадов регистра триггера запроса прерывания.

Вход MD (выбора режима) определяет один из 2-х режимов работы при наличии логического 0 на входе MD устройство работает в режиме ввода. В этом режиме выходные буферные каскады открыты когда устройство выбрано. Управление записью осуществляется сигналом по входу EW.

При наличии логической 1 на входе MD устройство работает в режиме вывода. В этом случае выходные буферные каскады независимо от выборки устройства.

Вход EW используется как синхросигнал для записи информации в регистр при MD=0 и для синхронной установки триггера запроса прерывания.

Условно-графическое обозначение микросхемы представлено на рисунке 3.

Рисунок 3 – Условно-графическое обозначение К589ИР12

Функциональные назначения выводов микросхемы К589ИР12 представлены в таблице 3.

Таблица 3 – Функциональные назначения выводов микросхемы К589 ИР12

Функциональное назначение

Стробирующий сигнал

Напряжение питания (+5 В)

Триггер запроса прерывания служит для выработки сигнала запроса прерывания в процессорной системе. При установке системы в исходное состояние низким уровнем сигнала CLR триггер запроса прерывания устанавливается в 1 (единица) т.е. данное устройство не требует прерывания. Одновременно с этим же сигналом происходит установка регистра в 0 (нуль). Принято что многорежимный буферный регистр находится в состоянии прерывания когда выходу INR соответствует логический 0 что позволяет обеспечить прямое соединение с входами запроса блока приоритетного прерывания.

При работе в режиме ввода (т.е. на входе MD сигнал низкого уровня) входной сигнал EW производит запись информации в регистр данных и установку триггера запроса в 0. Триггер запроса прерывания устанавливается в 1 при условии выбора устройства (так же вырабатывает сигнал прерывания на выходе INR).

Структурная схема микросхемы К589 ИР12 представлена на рисунке 4.

Рисунок 4 – Структурная схема К589 ИР12

Статические и динамические параметры представлены в таблице 5 и 6.

На рисунке 5 представлены функциональные схемы вариантов использования микросхемы.

Рисунок 5 – функциональные схемы применения К589 ИР12.

а) входной буферный регистр;

б) устройство прерывания;

в) выходной буферный регистр;

г) устройство двунаправленной передачи информации.

Таблица 4 – Статические параметры К589 ИР12

Ток потребления Icc мА

Входной ток низкого уровня при UIL = 055 В

Для входа CS1 I1H мкА (min)

Для входа MD I1H мкА (min)

Для остальных I1H мкА (min)

Входной ток низкого уровня при UIL = 525 В

Для входа CS1 I1H мкА

Для входа MD I1H мкА

Для остальных I1H мкА

Выходной ток высокого уровня в состоянии «выкл.»

Для Q1 – Q8 при UOH = 528 В IH мкА

Выходное напряжение низкого уровня при IH = 15 мА UOL В

Выходное напряжение высокого уровня при IH = - 1 мА UOН В (min)

Примечание: типовые значения тока потребления 90 мА выходное напряжение низкого уровня 04 В высокого – 40 В.

Таблица 5 – Динамические параметры К589 ИР12

Длительность импульсов

Время задержки распространения сигналов

От входа EW до выхода Q1 – Q8

От входа CLR до выхода Q1 – Q8

От входа D1 – D8 до выхода Q1 – Q8

От входа EW до выхода INR

От выходов CS1 и CS2 до выхода Q1 – Q8

Время установки информации на входах D1 – D8 относительно сигнала EW

Время сохранения информации

Время задержки перехода от входа CS1 до выхода Q1 – Q8

3 Функциональная схема узла

Функциональная схема узла индикации управляющего слова представлена на рисунке 6.

Рисунок 6 – Функциональная схема узла индикации

При работе данного узла в зависимости от значений на входах CS1 EW и CLR происходит считывание и вывод выходной информации из канала А на устройство индикации (автоматический режим при соединении EW с общей шиной) либо отображать информацию записываемую в канал А (ручной режим) в режимах 1 и 2 устройства ввода.

4 Описание принципиальной электрической схемы узла

Принципиальная электрическая схема представлена в приложении А.

В состав узла входят восемь светодиодов (индикаторов) в процессе работы которых формируется визуальное представление о процессах внутри канала А.

Также к светодиодам последовательно подключены резистивные элементы служащие дополнительной нагрузкой для узла.

Данная схема показывает последовательность соединения микросхемы К589ИР12 с элементами индикации (светодиоды).

Во время работы узла при поступлении сигнала на вход EW (соединение с общей шиной) узел переходит в автоматический режим при котором информация из канала А выводится на элементы индикации.

Режим ручного ввода позволяет отображать записываемую в канал А информацию при режимах 1 и 2. запись в регистр стробируется сигналом STB поступающим с устройства формирования сигналов (кнопка SA2 не указана) или с разряда CS канала В.

5 Расчет временных задержек в схеме функционального узла

Для расчета времени задержки необходимо при соединении микросхем суммировать значения времени задержек каждой из них.

При расчете временных задержек учитывая что в состав схемы входит всего одна микросхема КР589ИР12 принимаю за время задержки данные представленные в технической документации. Принимаю за основное время задержки время задержки между входными каналами D1 – D8 до выходных каналов Q1 – Q8 которое составляет 30 нс по паспортным данным.

6 Расчет мощности потребляемой функциональным узлом от источника питания.

При расчете мощности для данного узла принимаю значение входного потребляемого тока согласно техническим данным I = 130 мА при напряжении питания U = 525 В для К589ИР12 получаю мощность P:

При выполнении данной работы были получены навыки составления структурных и функциональных схем анализа сложных цифровых устройств усвоены основные понятия и термины относящиеся к проектированию электронных цифровых устройств и их сопряжению.

Были получены навыки поиска и использования необходимой научно-технической литературы и работы с ней а также получен опыт составления и оформления конструкторской документации.

При выполнении расчетно-графической работы решались задачи проектирования схем цифровых устройств применяемых в системах управления технологическим оборудованием и технологическими процессами в ЭВМ. Сформированы навыки и умения правильного выбора и применения имеющихся схемотехнических решений аппаратуры систем управления и ЭВМ необходимые для решения задач эксплуатации имеющихся и создание новых систем управления на их основе.

Список использованных источников

Микропроцессоры: в трех книгах. Книга 1: Архитектура и проектирование микроЭВМ. Организация вычислительных процессов: учебн. для втузов П.В. Нестеров [и др.]; под ред. Л.Н. Преснухина. – М.: Высш. шк. 1986. – 495 с.

Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Спрвочник. Т.5. – М.: КУбК-а 1997. 608 с.: ил.

Микропроцессорные автоматические системы регулирования. Основы теории и элементы: Учеб. пособие В.В. Солодовников В.Г. Коньков В.А. Суханов О.В. Шевяков; под ред. В.В. Солодовникова. – М.: Высш. шк. 1991. 225 с. ил.

Хвощ С.Т. Микропроцессоры и микроЭВМ в системах автоматического управления С.Т. Хвощ [и др.] – Л.: Машиностроение. Ленингр. отд-ние 1987. – 640 с.

Шило В.Л. Популярные цифровые микросхемы: Справочник 2-е изд.испр – Челябинск: Металлургия Челябинское отделение 19889. – 352с:ил. – (Массовая радиобиблиотека вып. 1111)

СТП 101-00. Общие требования и правила оформления выпускных квалификационных работ курсовых проектов (работ) отчетов по РГР по УИРС по производственной практике и рефератов. – Взамен СТП 2069022.101-88 СТП 2069022.102-93 СТП 2069022.103-92 СТП 2069022.105-95 СТП 2069022.108-93: введ. 2000-12-25. – Оренбург: ОГУ 2000. – 62 с.

ГОСТ 2.708-81. ЕСКД. Правила выполнения электрических схем цифровой вычислительной техники. – Взамен ГОСТ 2.708-72; введ. 1982-01-01. – М.: Издательство стандартов 1986. – 16 с.

ГОСТ 2.710-81. ЕСКД. Обозначения буквенно-цифровые в электрических схемах. – Взамен ГОСТ 2.710-75; введ. 1981-07-01. – М.: Издательство стандартов 1985. – 14 с.

ГОСТ 2.721-74. ЕСКД. Обозначения условно-графические в схемах. Обозначения общего применения. – Взамен ГОСТ 2.721-68 ГОСТ 2.783-69; введ. 1975-07-01. – М.: Издательство стандартов 1983. – 22 с.

ГОСТ 2.730-73. ЕСКД. Обозначения условно-графические в схемах. Приборы полупроводниковые. - Взамен ГОСТ 2.730-68; введ. 1974-07-01. – М.: Издательство стандартов 1983. – 28 с.

ГОСТ 2.743-91. ЕСКД. Обозначения условно-графические в схемах. Элементы цифровой техники. - Взамен ГОСТ 2.743-82; введ. 1993-01-01. – М.: Издательство стандартов 1995. – 35 с.

Модуль УМПК-80МИ2. Паспорт ПБА3.660.225 ПС.

Модуль УМПК-80МИ2. Схема электрическая принципиальная ПБА3.660.225 Э3.

Модуль УМПК-80МИ2. Перечень элементов ПБА3.660.223 ПЭ3.

Рекомендуемые чертежи

- 25.01.2023